DSEIII (PlasmaTherm/Deep Silicon Etcher): Difference between revisions

Text replacement - "/wiki/index.php/" to "/wiki/index.php?title=" |

→Detailed Specifications: removed N2 |

||

| (13 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

{{ |

{{tool2|{{PAGENAME}} |

||

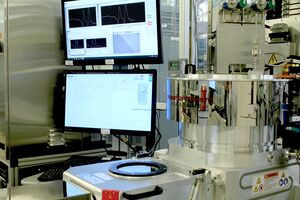

|picture=DSEIII.jpg |

|picture=DSEIII.jpg |

||

|type |

|type= Dry Etch |

||

|super= |

|super= Aidan Hopkins |

||

|super2= Tony Bosch |

|||

|phone= 805-893- |

|phone= 805-893-3486 |

||

|location=Bay 2 |

|location=Bay 2 |

||

|email= |

|email=bosch@ece.ucsb.edu |

||

|description |

|description= Deep Silicon Etcher: Bosch MEMS Processes |

||

|manufacturer |

|manufacturer= Plasmatherm |

||

|materials |

|materials= |

||

|model= DSE-iii |

|||

|toolid=63 |

|toolid=63 |

||

}} |

}} |

||

==About== |

==About== |

||

The Si DRIE system is a Plasma-Therm DSEIII series system with a loadlock. The system has an Inductively Coupled Plasma (ICP) coil and a capactively coupled substrate HF (13.56MHz) and LF (100kHz) supplies to independently control plasma density and ion energy in the system. This system is dedicated to deep silicon Bosch etching, although short O2 etches are also permitted. |

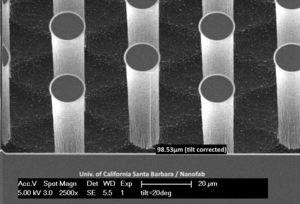

The Si DRIE system is a Plasma-Therm DSEIII series system with a loadlock, intended for Standard [https://en.wikipedia.org/wiki/Deep_reactive-ion_etching#Bosch_process Bosch etching] (cycling Dep/Etch sequence) for high aspect-ratio, high-selectivity deep Silicon etching. The system has an Inductively Coupled Plasma (ICP) coil and a capactively coupled substrate HF (13.56MHz) and LF (100kHz) supplies to independently control plasma density and ion energy in the system. This system is dedicated to deep silicon Bosch etching, although short O2 etches are also permitted. [[File:DSEiii Bosch Ecth SEM Example 01.png|alt=Example SEM image|thumb|300x300px|Example of 100µm Deep Bosch Etched Silicon posts with hard mask. (Image Credit: Demis D. John, Jul. 2021)]] |

||

The fixturing is configured for 4" diameter Si wafers and uses a clamp to hold the wafer on the RF chuck. Smaller pieces are placed on a 4-inch wafer carrier for etching. |

|||

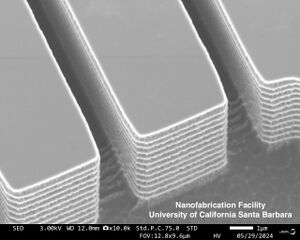

[[File:DSEiii Example Bosch Etch 02.jpg|alt=SEM of 10µm deep bosch etched trenches|thumb|Example of 10µm deep Bosch etch, showing horizontal striations from each etch cycle. (Image Credit: Biljana Stamenic, May 2024)]] |

|||

The materials allowed to be exposed in the system are limited to Silicon, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>X</sub>N<sub>Y</sub>, and polymer films such as photoresist, PMMA, and polyimide. Other materials can be placed in the chamber with staff approval. |

The materials allowed to be exposed in the system are limited to Silicon, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>X</sub>N<sub>Y</sub>, and polymer films such as photoresist, PMMA, and polyimide. Other materials can be placed in the chamber with staff approval. |

||

Helium back-side cooling is used to keep the sample cool during the etch. Temperature control is very important as the polymer passivation layer is chemically etched away by the fluorine gas at elevated temperatures, resulting in loss of profile control. |

Helium back-side cooling is used to keep the sample cool during the etch. Temperature control is very important as the polymer passivation layer is chemically etched away by the fluorine gas at elevated temperatures, resulting in loss of profile control. For pieces mounted to carriers, it might be important to use an adhesive for uniform temperature - contact supervisor for options. |

||

| ⚫ | |||

| ⚫ | |||

| ⚫ | |||

The etch rate is dependent on the open area of silicon (macro-loading effect) with large open area samples etching slower than small open area samples. Features with a high aspect ratio will also etch slower than more open areas. This is known as RIE lag or the micro-loading effect. |

The etch rate is dependent on the open area of silicon (macro-loading effect) with large open area samples etching slower than small open area samples. Features with a high aspect ratio will also etch slower than more open areas. This is known as RIE lag or the micro-loading effect. |

||

The in-situ laser monitor installed on this system allows for repeatable etches and endpoint detection via continuous optical monitoring of the wafer reflectivity in a user-determined location, through a porthole on the chamber. |

The in-situ laser monitor installed on this system allows for repeatable etches and endpoint detection via continuous optical monitoring of the wafer reflectivity in a user-determined location, through a porthole on the chamber. |

||

==Detailed Specifications== |

==Detailed Specifications== |

||

*3500 W ICP coil power at 2 MHz and 500 W substrate bias at 13.56 MHz plasma generators |

*3500 W ICP coil power at 2 MHz and 500 W substrate bias at 13.56 MHz plasma generators |

||

*C<sub>4</sub>F<sub>8</sub>, SF<sub>6</sub>, |

*C<sub>4</sub>F<sub>8</sub>, SF<sub>6</sub>, CF<sub>4</sub>, O<sub>2</sub>, Ar gases available |

||

*He-back-side cooling |

*He-back-side cooling |

||

*100mm wafer held down with ceramic clamp., single-load |

*100mm wafer held down with ceramic clamp., single-load |

||

**Users must ensure thick photoresists or other substances do not contact the clamp, to prevent wafer stiction and breakage. |

**Users must ensure thick photoresists or other substances do not contact the clamp, to prevent wafer stiction and breakage. |

||

*Windows-based Cortex software control of process and wafer handling |

*Windows-based Cortex software control of process and wafer handling |

||

*Allowed materials: Silicon, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>X</sub>N<sub>Y</sub>, Al, Al2O3, and polymer films such as photoresist, PMMA, and polyimide; CrystalBond wax for mounting to carrier wafer |

*Allowed materials: Silicon, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>X</sub>N<sub>Y</sub>, Al, Al2O3, and polymer films such as photoresist, PMMA, and polyimide; Ask staff before using: CrystalBond wax or Santovac oil for mounting to carrier wafer. Dicing tape allowed with staff training. |

||

**Realized etch rates (including passivation steps) for Bosch process of >8 um / min. Selectivity to resist > 80:1 for low aspect ratio. |

**Realized etch rates (including passivation steps) for Bosch process of >8 um / min. Selectivity to resist > 80:1 for low aspect ratio. |

||

*Laser monitoring with camera and etch simulation software: [[Laser Etch Monitoring|Intellemetrics LEP 500]] |

*Laser monitoring with camera and etch simulation software: [[Laser Etch Monitoring|Intellemetrics LEP 500]] |

||

==Documentation== |

==Operation Procedures & Documentation== |

||

* |

*[[Media:PT-DSEiii - Running a process.pdf|DSEIII Operating Instructions]] |

||

*[[Laser Etch Monitoring|Laser Etch Monitoring procedures]] |

*[[Laser Etch Monitoring|Laser Etch Monitoring procedures]] |

||

===Preventing Wafer Breakage=== |

|||

| ⚫ | |||

| ⚫ | |||

See this page for Edge-Bead Removal techniques: [[Photolithography - Manual Edge-Bead Removal Techniques|'''Manual Edge-Bead Removal Techniques''']] |

|||

'''Remove at least 7mm around ALL of the outer edge of the 4-inch wafer. Do not try to save die by removing less, or you will lose the whole wafer and require the chamber to be vented.''' |

|||

| ⚫ | Pieces of wafers can be placed onto 4" silicon wafers, or mounted as long as material does not get on the clamp. It is common for through-silicon etches to use a carrier wafer, often bonded with wax on the [[Wafer Bonder (Logitech WBS7)|Logitech bonder]], and excess wax carefully removed to ensure not adhesion to the clamp. |

||

==Recipes== |

==Recipes== |

||

*[https://wiki.nanotech.ucsb.edu/ |

*[https://wiki.nanotech.ucsb.edu/w/index.php?title=ICP_Etching_Recipes#DSEIII_.28PlasmaTherm.2FDeep_Silicon_Etcher.29 '''Plasma-Therm DSE-iii Recipes'''] - Recipes specific to this tool. |

||

**Plasma Dicing / Through-silicon Via etch process, using UV-release Dicing tape for full wafers, or wax for small pieces. |

|||

*All [[Dry Etching Recipes]] - use this list to see other options for dry etching various materials. |

*All [[Dry Etching Recipes]] - use this list to see other options for dry etching various materials. |

||

*Online Training Video: |

|||

**[https://gauchocast.hosted.panopto.com/Panopto/Pages/Viewer.aspx?id=55a26021-b299-41cc-a512-ae23010845aa <u>Plasmatherm DSE-iii Training</u>] |

|||

**'''Important:''' ''This video is for reference only, and does not give you authorization to use the tool. You must be officially authorized by the supervisor before using this machine.'' |

|||

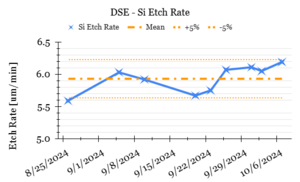

== Process Control Data == |

|||

*Recipe: ''STD_Bosch_Si (⭐️Production),'' on 100mm Si Wafer with ~50% open area, photoresist mask, ~40µm deep |

|||

*[https://docs.google.com/spreadsheets/d/1xQcdUH560nT928miZMeP7xxQSwHz_a_EB9s_Kb1LSfg/edit?gid=0#gid=0 Si Etching with C<sub>4</sub>F<sub>8</sub>/SF<sub>6</sub>/Ar - '''Etch Data'''] |

|||

*[https://docs.google.com/spreadsheets/d/1xQcdUH560nT928miZMeP7xxQSwHz_a_EB9s_Kb1LSfg/edit?gid=1804752281#gid=1804752281 Si Etching with C<sub>4</sub>F<sub>8</sub>/SF<sub>6</sub>/Ar - '''Plots'''][[File:DSE plot.png|alt=example of Process Control Charts|none|thumb|[https://docs.google.com/spreadsheets/d/1xQcdUH560nT928miZMeP7xxQSwHz_a_EB9s_Kb1LSfg/edit?gid=1804752281#gid=1804752281 Click for Process Control Charts]|link=https://docs.google.com/spreadsheets/d/1xQcdUH560nT928miZMeP7xxQSwHz_a_EB9s_Kb1LSfg/edit?gid=1804752281#gid=1804752281]] |

|||

{| |

|||

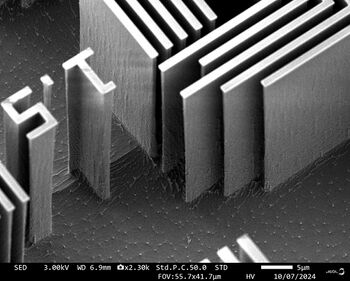

|[[File:Plasmatherm DSE - 40um deep Si etch Cal 241007 - 30D 002.jpg|alt=Tilted SEM of 40um deep etch|none|thumb|350x350px|~40µm deep Silicon etch, run as Process Control "EtchCal" (''Process Development and Image: [[Noah Dutra]], 2024-10-07'')]] |

|||

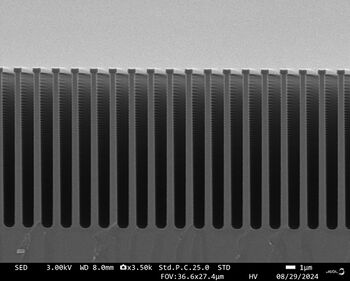

|[[File:Copy of 22 013 (1).jpg|alt=Example SEM image|none|thumb|350x350px|Example of 16.32µm Deep Etched Silicon with UV6 Photoresist mask, 2µm Pitch. (''Image Credit: [[Noah Dutra]] 2024-08'')]] |

|||

|} |

|||

Latest revision as of 00:09, 11 December 2025

| ||||||||||||||||||||||||||||||||

About

The Si DRIE system is a Plasma-Therm DSEIII series system with a loadlock, intended for Standard Bosch etching (cycling Dep/Etch sequence) for high aspect-ratio, high-selectivity deep Silicon etching. The system has an Inductively Coupled Plasma (ICP) coil and a capactively coupled substrate HF (13.56MHz) and LF (100kHz) supplies to independently control plasma density and ion energy in the system. This system is dedicated to deep silicon Bosch etching, although short O2 etches are also permitted.

The fixturing is configured for 4" diameter Si wafers and uses a clamp to hold the wafer on the RF chuck. Smaller pieces are placed on a 4-inch wafer carrier for etching.

The materials allowed to be exposed in the system are limited to Silicon, SiO2, Si3N4, SiOXNY, and polymer films such as photoresist, PMMA, and polyimide. Other materials can be placed in the chamber with staff approval.

Helium back-side cooling is used to keep the sample cool during the etch. Temperature control is very important as the polymer passivation layer is chemically etched away by the fluorine gas at elevated temperatures, resulting in loss of profile control. For pieces mounted to carriers, it might be important to use an adhesive for uniform temperature - contact supervisor for options.

The etch rate is dependent on the open area of silicon (macro-loading effect) with large open area samples etching slower than small open area samples. Features with a high aspect ratio will also etch slower than more open areas. This is known as RIE lag or the micro-loading effect.

The in-situ laser monitor installed on this system allows for repeatable etches and endpoint detection via continuous optical monitoring of the wafer reflectivity in a user-determined location, through a porthole on the chamber.

Detailed Specifications

- 3500 W ICP coil power at 2 MHz and 500 W substrate bias at 13.56 MHz plasma generators

- C4F8, SF6, CF4, O2, Ar gases available

- He-back-side cooling

- 100mm wafer held down with ceramic clamp., single-load

- Users must ensure thick photoresists or other substances do not contact the clamp, to prevent wafer stiction and breakage.

- Windows-based Cortex software control of process and wafer handling

- Allowed materials: Silicon, SiO2, Si3N4, SiOXNY, Al, Al2O3, and polymer films such as photoresist, PMMA, and polyimide; Ask staff before using: CrystalBond wax or Santovac oil for mounting to carrier wafer. Dicing tape allowed with staff training.

- Realized etch rates (including passivation steps) for Bosch process of >8 um / min. Selectivity to resist > 80:1 for low aspect ratio.

- Laser monitoring with camera and etch simulation software: Intellemetrics LEP 500

Operation Procedures & Documentation

Preventing Wafer Breakage

It is very important that your wafer does not stick to the top-side clamp in the chamber. The clamp will get hot during long etches, causing thick photoresists to soften and adhere to the clamp, resulting if wafer loss and breakage.

Users must remove photoresist from the wafer edge to prevent this. We have photolithographic methods for performing this cleanly, or simple swabbing with EBR100 also works well.

See this page for Edge-Bead Removal techniques: Manual Edge-Bead Removal Techniques

Remove at least 7mm around ALL of the outer edge of the 4-inch wafer. Do not try to save die by removing less, or you will lose the whole wafer and require the chamber to be vented.

Pieces of wafers can be placed onto 4" silicon wafers, or mounted as long as material does not get on the clamp. It is common for through-silicon etches to use a carrier wafer, often bonded with wax on the Logitech bonder, and excess wax carefully removed to ensure not adhesion to the clamp.

Recipes

- Plasma-Therm DSE-iii Recipes - Recipes specific to this tool.

- Plasma Dicing / Through-silicon Via etch process, using UV-release Dicing tape for full wafers, or wax for small pieces.

- All Dry Etching Recipes - use this list to see other options for dry etching various materials.

- Online Training Video:

- Plasmatherm DSE-iii Training

- Important: This video is for reference only, and does not give you authorization to use the tool. You must be officially authorized by the supervisor before using this machine.

Process Control Data

- Recipe: STD_Bosch_Si (⭐️Production), on 100mm Si Wafer with ~50% open area, photoresist mask, ~40µm deep

- Si Etching with C4F8/SF6/Ar - Etch Data

- Si Etching with C4F8/SF6/Ar - Plots

Click for Process Control Charts

|

|